# Three-Axis Magnetic Sensor

#### 1 Product Overview

The VCM1193L is a three-axis magnetic sensor with very low power consumption developed specifically for Drone Nevigation. This surface-mount, small sized chip has integrated magnetic sensors with signal condition ASIC, it offers the advantages of low noise, high accuracy, low power consumption, offset cancellation.

The VCM1193L is based on Anisotropic Magneto-Resistive (AMR) and CMOS technology, Linear three axis magnetic sensor along with custom-designed 16-bit ADC and power management ASIC, it provides digital signal with I<sup>2</sup>C serial bus.

The VCM1193L is in a 3x3x0.9mm3 surface mount 16-pin land grid array (LGA) package.

## 2 Key Features

| Features                                                                                                                                                     | Benefits                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| 3-Axis Magneto-Resistive Sensors in a 3x3x0.9 mm3 Land Grid Array Package (LGA), guaranteed to operate over an extended temperature range of -40°C to +85°C. | Small Size for Highly Integrated Products. Signals Have Been Digitized And Calibrated.           |

| 16 Bit ADC With Low Noise AMR Sensors Achieves 2 Milli-Gauss Field Resolution                                                                                | Enables 1° to 2° Degree Compass Heading Accuracy ,<br>Allows for Navigation and LBS Applications |

| Wide Magnetic Field Range (±8 Gauss)                                                                                                                         | Maximizes Sensor's Full Dynamic Range and Resolution                                             |

| I2C (Standard ,Fast Modes) Interface.                                                                                                                        | High Speed Digital Output                                                                        |

| Low Operation Voltage (2.16V To 3.6V) and Low Power Consumption                                                                                              | Compatible with Battery Powered Applications                                                     |

| Lead Free Package Construction                                                                                                                               | RoHS Compliance                                                                                  |

| Software And Algorithm Support Available                                                                                                                     | Compassing Heading, Hard Iron, Soft Iron, and Auto<br>Calibration Libraries Available            |

## 3 Applications

| Traffic Detection    | Typical Applications Include Geomagnetic vehicle speed and traffic volume                 |

|----------------------|-------------------------------------------------------------------------------------------|

| Consumer Electronics | Typical Applications Include Door Lock Position Detection, Sweeper Direction Control, etc |

| Navigation           | Typical Applications Include Auto Navigation Systems, and Medical Navigation Devices etc  |

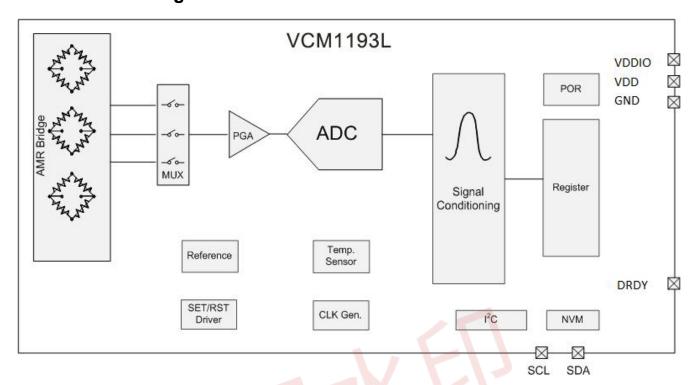

# 4 Module/Circuit Diagra

Figure 1. Block Diagram

Table 1. Block Function

| Block               | Function                                                                                |  |  |  |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| AMR Bridge          | 3 axis magnetic sensor                                                                  |  |  |  |  |  |  |  |

| MUX                 | Multiplexer for sensor channels                                                         |  |  |  |  |  |  |  |

| PGA                 | Programmable gain amplifier for sensor signals                                          |  |  |  |  |  |  |  |

| ADC                 | 16bit Analog-to-Digital converter                                                       |  |  |  |  |  |  |  |

| Signal Conditioning | Digital blocks for magnetic signal calibration and compensation                         |  |  |  |  |  |  |  |

| I <sup>2</sup> C    | Interface logic data I/O                                                                |  |  |  |  |  |  |  |

| NVM                 | Non-Volatile memory for calibrated parameters                                           |  |  |  |  |  |  |  |

| SET/RST Driver      | Internal driver to initialize magnetic sensor                                           |  |  |  |  |  |  |  |

| Reference           | Voltage/Current reference for internal biasing                                          |  |  |  |  |  |  |  |

| Clock Gen.          | Internal oscillator for internal operation                                              |  |  |  |  |  |  |  |

| POR                 | Power on reset                                                                          |  |  |  |  |  |  |  |

| Temperature Sensor  | Temperature sensor for internal sensitivity/offset compensation, and temperature output |  |  |  |  |  |  |  |

# **5 Absolute Maximum Ratings**

Table 2. Absolute Maximum Ratings (Tested at 25°C except stated otherwise.)

| Parameter                                  | MIN.         | MAX.           | Units    |  |  |  |

|--------------------------------------------|--------------|----------------|----------|--|--|--|

| VDDIO                                      | -0.3         | 5.4            | V        |  |  |  |

| VDD                                        | -0.3         | 5.4            | V        |  |  |  |

| Storage Temperature                        | -40          | 125            | °C       |  |  |  |

| Exposed to Magnetic Field (all directions) | - 50000 Gaus |                |          |  |  |  |

| Reflow Classification                      | MSL 3,       | 260°C Peak Tem | perature |  |  |  |

### **6 Electrical Performance**

Table 3. Specifications (\* Tested and specified at 25°C except stated otherwise.)

| Parameter                               | Condition                                            | ıs                              | Min         | Тур   | Max | Unit            |

|-----------------------------------------|------------------------------------------------------|---------------------------------|-------------|-------|-----|-----------------|

| Supply Voltage                          | VDD                                                  |                                 | 2.16        |       | 3.6 | V               |

| I/O Voltage                             | VDDIO                                                |                                 | 1.65        | -     | 3.6 | V               |

| Standby                                 | Total cur                                            | rent on VDD and VDDIO           | 7-1-        | 5     | \ - | uA              |

|                                         |                                                      | ODR = 10Hz, A=0Dh               | <i>//</i> - | 150   | -   | μΑ              |

| Committee Committee                     | Normal<br>Mode                                       | ODR = 50Hz, A=09h               | - "         | 350   | -   | uA              |

| Supply Current                          | Wiode                                                | ODR = 100Hz, A=05h              | -           | 500   | -   | uA              |

|                                         | A=01h,B:                                             | =0x03 <mark>h,ODR</mark> =200Hz | -           | 1000  | -   | uA              |

| Sensor Field<br>Range                   | Full Scale                                           |                                 | -8          | -     | +8  | Gauss           |

| Sensitivity [1]                         | Field Rar                                            | nge = ±8G                       | -           | 3000  | -   | LSB/G           |

| Linearity<br>(Best fit linear<br>curve) | Field Rar                                            | nge = ±8G                       | -           | 0.1   | -   | %FS             |

| Hysteresis                              | All Range                                            | es                              | -           | 0.1   | -   | %FS             |

| Cross Axis<br>Sensitivity               |                                                      | ld = 1 Gauss,<br>= ±2 Gauss     | -           | 0.1   | -   | %/G             |

| Offset                                  | -                                                    |                                 | -           | ±10   | -   | mG              |

| Sensitivity<br>Tempco                   | Ta = -40°                                            | 'C~85°C                         | -           | ±0.05 | -   | %/°C            |

| Total Peak to<br>Peak Noise             | -                                                    |                                 | -           | 1     | -   | mG              |

| Digital Resolution                      | Change \                                             | with Gain                       | 0.1         |       | 1.0 | mGauss          |

| Field Resolution                        | Standard<br>±2G                                      | deviation 100 Data, FS          | -           | 2     | -   | mGauss          |

| Output Data Rate                        | Output Data Rate Programmable. 10Hz/50Hz/100Hz/200Hz |                                 |             |       |     | Samples/<br>sec |

| X-Y-Z<br>Orthogonality                  | Sensitivit<br>Direction                              |                                 | -           | 90±1  | -   | degree          |

| Parameter                | Conditions          | Min  | Тур | Max | Unit |

|--------------------------|---------------------|------|-----|-----|------|

| Operating<br>Temperature | -                   | -40  | -   | 85  | °    |

| ECD                      | HB Model            | 5500 | -   | -   | V    |

| ESD                      | Charge Device Model | 750  | -   | -   | V    |

Note [1]: Sensitivity is calibrated at zero field, it is slightly decreased at high fields.

## 7 I/O Characteristics

Table 4. I/O Characteristics

| Parameter                     | Symbol | Pin      | Condition                                                     | Min.      | TYP. | Max.      | Unit |

|-------------------------------|--------|----------|---------------------------------------------------------------|-----------|------|-----------|------|

| Voltage Input<br>High Level 1 | VIH1   | SDA, SCL | -                                                             | 0.7*VDDIO | ) )  | VDDIO+0.3 | V    |

| Voltage Input<br>Low Level 1  | VIL1   | SDA, SCL | -                                                             | -0.3      | -    | 0.3*VDDIO | V    |

| Voltage Output<br>High Level  | VOH    | INT      | Output Current ≥-<br>100uA                                    | 0.8*VDDIO | -    | 1         | V    |

| Voltage Output<br>Low Level   | VOL    | INT, SDA | Output Current<br>≤100uA(INT)<br>Output Current<br>≤1mA (SDA) |           |      | 0.2*VDDIO | V    |

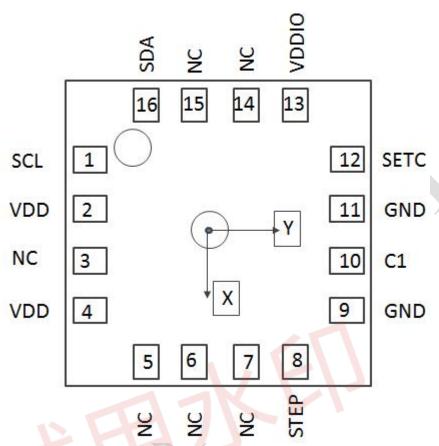

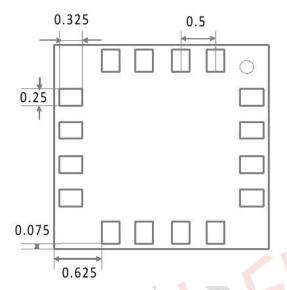

# 8 Package Pin Configurations

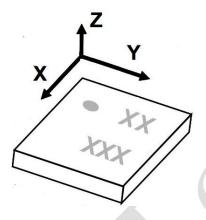

## 8.1 Package 3-D View

Arrow indicates direction of magnetic field that generates a negative output reading in normal measurement configuration.

Figure 2. Package 3-D View

**Table 5. Pin Configurations**

| PIN No. | PIN NAME | Function                                                 |

|---------|----------|----------------------------------------------------------|

| 1       | SCL      | Serial Clock – I <sup>2</sup> C Master/Slave Clock       |

| 2       | VDD      | Power Supply (2.16V to 3.6V)                             |

| 3       | NC       | Not to be Connected                                      |

| 4       | VDD      | Power supply                                             |

| 5       | NC       | Not to be Connected                                      |

| 6       | NC       | Not to be Connected                                      |

| 7       | NC       | Not to be Connected                                      |

| 8       | SETP     | Set/Reset Strap Positive – S/R Capacitor (C2) Connection |

| 9       | GND      | Supply Ground                                            |

| 10      | C1       | Reservoir Capacitor (C1) Connection                      |

| 11      | GND      | Supply Ground                                            |

| 12      | SETC     | S/R Capacitor (C2) Connection – Driver Side              |

| 13      | VDDIO    | IO Power Supply (1.71V to VDD)                           |

| 14      | NC       | Not to be Connected                                      |

| 15      | NC       | Not to be Connected                                      |

| 16      | SDA      | Serial Data – I <sup>2</sup> C Master/Slave Data         |

Figure 3. TOP VIEW (looking through)

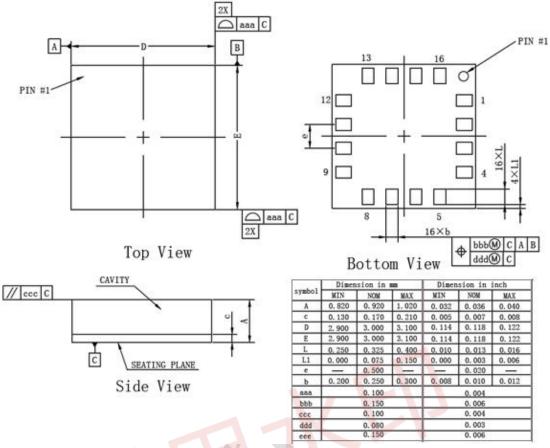

## 8.2 Package Outlines

### 8.2.1 Package Type

LGA (Land Grid Array)

### 8.2.2 Package Size:

3mm (Length)\*3mm (Width)\*0.9mm (Height)

Figure 4. Package Size

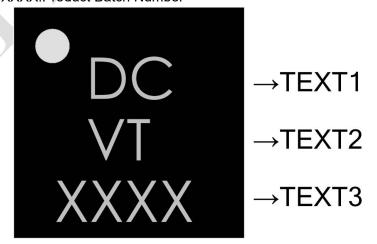

### 8.2.3 **Marking**:

Tracking code:

Text1: D-Fixed code, C:Version

Text2: VT:Vtran logo

Text3: XXXX:Product Batch Number

Figure 5. Chip Marking

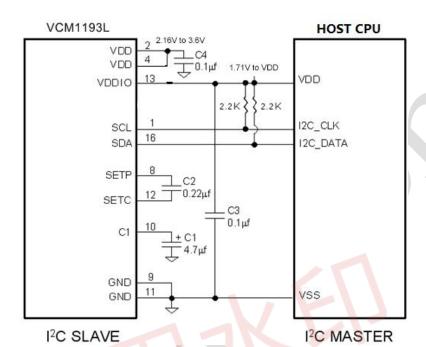

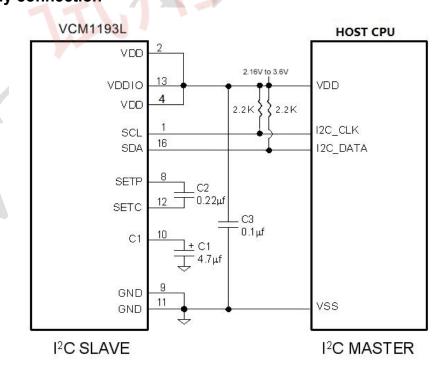

### 9 External Connection

## 9.1 Dual Supply Connection

Figure 6. Dual Supply Connection

## 9.2 Single Supply connection

Figure 7. Single Supply Connection

### 9.3 Mounting Considerations

The following is the recommend printed circuit board (PCB) footprint for the VCM1193L. Due to the fine pitch of the pads, the footprint should be properly centered in the PCB.

Figure 8. VCM1193L PCB footprint

### 9.4 Layout Considerations

Besides keeping all components that may contain ferrous materials (nickel, etc.) away from the sensor on both sides of the PCB, it is also recommended that there is no conducting copper line under/near the sensor in any of the PCB layers.

#### 9.4.1 Solder Paste

A 4 mil stencil and 100% paste coverage is recommended for the electrical contact pads.

#### 9.4.2 Reflow Assembly

This device is classified as MSL 3 with 260°C peak reflow temperature. As specified by JEDEC, parts with an MSL 3 rating require baking prior to soldering, if the part is not kept in a continuously dry (< 10% RH) environment before assembly. Reference IPC/JEDEC standard J-STD-033 for additional information.

No special reflow profile is required for VCM1193L, which is compatible with lead eutectic and lead-free solder paste reflow profiles. VTRAN recommends adopting solder paste manufacturer's guidelines. Hand soldering is not recommended.

#### 9.4.3 External Capacitors

The external capacitors C1 should be ceramic type with low ESR characteristics. The exact ESR value is not critical, but values less than 200 milli-ohms are recommended. Reservoir capacitor C1 is nominally 4.7  $\mu$ F in capacitance, with the set/reset capacitor C2 nominally 0.22  $\mu$ F in capacitance. Low ESR characteristics may not be in many small SMT ceramic capacitors (0402), so be prepared to up-size the capacitors to gain low ESR characteristics.

## 10 Basic Device Operation

### 10.1 Anisotropic Magneto-Resistive Sensors

The VCM1193L magneto-resistive sensor circuit consists of tri-axial sensors and application specific support circuits to measure magnetic fields. With a DC power supply is applied to the sensor two terminals, the sensor converts any incident magnetic field in the sensitive axis directions to a differential voltage output. The ASIC then amplifies and processes the signal to have a digital output.

The device has an offset cancellation function to eliminate sensor and ASIC offsets. It also applies a self-aligned magnetic field to restore magnetic state before each measurement to ensure high accuracy. Because of these features, the VCM1193L doesn't need to calibrate every time in most of application situations. It may need to be calibrated once in a new system or a system changes a new battery.

### 10.2 Power Management

There are two power supply pins to the device. VDD provides power for all the internal analog and digital functional blocks. VDDIO provides power for digital I/O and logic. It is possible to work with VDDIO equal to VDD, the single supply mode, or with VDDIO lower than VDD, the dual supply mode.

The device should turn-on both power pins in order to operate properly. When the device is powered on, all registers are reset by POR, then the device transits to the standby mode and waits for further commands.

Table 6 provides references for four power states. Transitions between power state 2 and power state 3 are prohibited, due to leakage current concerns.

Power State **VDD VDDIO** Power State description 1 0V 0V Device Off, No Power Consumption Device Off, Unpredictable Leakage Current on 2 0V 1.65v~3.6v VDD due to Floating Node. Device Off, Same Current as Standby Mode 3 2.16v~3.6v 0 Device On, Normal Operation Mode, Enters 1.65v~3.6v 4 2.16v~3.6v Standby Mode after POR

**Table 6: Power States**

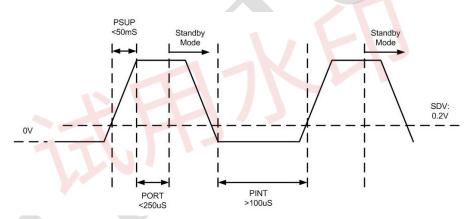

#### 10.3 Power On/Off Time

|                        |        |                                                                                                                     | ,    |      |      |      |

|------------------------|--------|---------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Parameter              | Symbol | Condition                                                                                                           | Min. | Тур. | Max. | Unit |

| POR Completion<br>Time | PORT   | Time Period After VDD and VDDIO at Operating Voltage to Ready for I <sup>2</sup> C Command and Analogy Measurement. | -    | -    | 350  | μs   |

| Power off<br>Voltage   | SDV    | Voltage that Device Considers to be Power Down.                                                                     | -    | -    | 0.2  | V    |

| Power on<br>Interval   | PINT   | Time Period Required for Voltage Lower Than SDV to Enable Next POR                                                  | 100  | -    | -    | μs   |

Table 7. Time Required for Power On/Off

After the device is powered on, some time periods are required for the device fully functional. The external power supply requires a time period for voltage to ramp up (PSUP), it is typically 50 milli-second. However it isn't controlled by the device. The Power-On-Reset time period (PORT) includes time to reset all the logics, load values in NVM to proper registers, enter the standby mode and get ready for analogy measurements. The power on/off time related to the device is in Table 7.

Figure 9. Power On/Off Timing

#### 10.4 Communication Bus Interface I<sup>2</sup>C

This device will be connected to a serial interface bus as a slave device under the control of a master device, such as the processor. Control of this device is carried out via I<sup>2</sup>C.

This device is compliant with I<sup>2</sup>C-Bus Specification, document number: 9398 393 40011. As an I<sup>2</sup>C compatible device, this device has a 7-bit serial address and supports I<sup>2</sup>C protocols. This device supports standard and fast speed modes, 100kHz and 400kHz, respectively. External pull-up resistors are required to support all these modes.

#### 10.5 Internal Clock

The device has an internal clock for internal digital logic functions and timing management. This clock is not available to external usage.

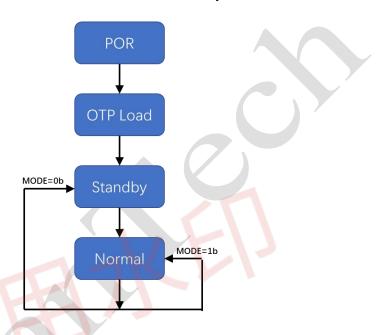

## 11 Modes Of Operation

#### 11.1 Modes Transition

The device has two different operational modes, controlled by register bit 'MODE'. The main purpose of the two modes is for power management. The modes can be transited to each other, as shown below, through I<sup>2</sup>C commands of changing mode bits. The default mode is Standby.

Figure 10. Operation Flow

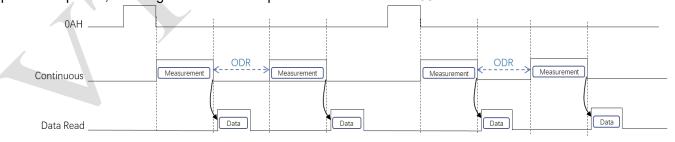

#### 11.2 Read Sequence

Complete magnetometer data read-out can be done as follow steps.

♦ Data protection, if any of the six data register is accessed, data protection starts. During Data protection period, data register cannot be updated until the last bits 05H have been read.

Figure 4. Normal Read Sequence

#### 11.3 Standby Mode

Standby mode is the default state of VCM1193L upon Power on POR and soft reset. In this mode, some block are in normal working state, which make sure the switching mode quickly. In this state, register values are hold on by a low power manager, I<sup>2</sup>C interface can be woken up by reading or writing any registers. There is no magnetometer measurement in the Standby mode. Internal clocking is also halted.

## 12 Application Examples

### 12.1 Measurement Example

- ♦ Write register 0AH by 0x0xh.

- ♦ Read data register 00H ~ 05H.

### 12.2 Standby Example

♦ Write Register 0AH by 0x00

## 12.3 Soft Reset Example

♦ Write Register 0BH by 0x80

# 13 I<sup>2</sup>C COMMUNICATION PROTOCOL

## 13.1 I<sup>2</sup>C Timings

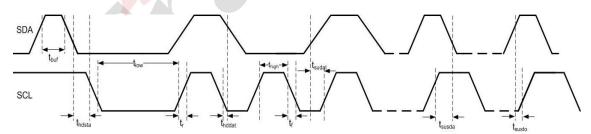

Below table and graph describe the I<sup>2</sup>C communication protocol times

Table 8. I<sup>2</sup>C Timings

| Parameter                | Symbol | Condition | Min. | Тур.  | Max. | Unit |

|--------------------------|--------|-----------|------|-------|------|------|

| SCL Clock                | fscl   | -         | 0    | -     | 400  | kHz  |

| SCL Low Period           | tlow   | -         | 1    | -     |      | μs   |

| SCL High Period          | thigh  | -         | 1    | -     |      | μs   |

| SDA Setup Time           | tsudat | -         | 0.1  | -     |      | μs   |

| SDA Hold Time            | thddat | -         | 0    |       | 0.9  | μs   |

| Start Hold Time          | thdsta | -         | 0.6  | (/- ) | -    | μs   |

| Start Setup Time         | tsusta | -         | 0.6  | -     | -    | μs   |

| Stop Setup Time          | tsusto | -         | 0.6  |       | -    | μs   |

| New Transmission<br>Time | tbuf   | -         | 1.3  | -     | -    | μs   |

| Rise Time                | tr     | -         | -    |       | _    | μs   |

| Fall Time                | tf     | 1-        | -    | -     | -    | μs   |

Figure 11. I2C Timing Diagram

### 13.2 I2C R/W Operation

#### 13.2.1 Abbreviation

Table 9. Abbreviation

| SACK | Acknowledged by slave      |

|------|----------------------------|

| MACK | Acknowledged by master     |

| NACK | Not acknowledged by master |

| RW   | Read/Write                 |

#### 13.2.2 Start/Stop/ACK

START: Data transmission begins with a high to transition on SDA while SCL is held high. Once I<sup>2</sup>C transmission starts, the bus is considered busy.

STOP: STOP condition is a low to high transition on SDA line while SCL is held high.

ACK: Each byte of data transferred must be acknowledged. The transmitter must release the SDA line during the acknowledge pulse while the receiver mush then pull the SDA line low so that it remains stable low during the high period of the acknowledge clock cycle.

NACK: If the receiver doesn't pull down the SDA line during the high period of the acknowledge clock cycle, it's recognized as NACK by the transmitter.

#### 13.2.3 I2C Address

The default I<sup>2</sup>C Address is OC: 0001100.

More I<sup>2</sup>C Address can be obtained through factory change.

#### 13.2.4 I2C Write

I<sup>2</sup>C write sequence begins with start condition generated by master followed by 7 bits slave address and a write bit (R/W=0). The slave sends an acknowledge bit (ACK=0) and releases the bus. The master sends the one byte register address. The slave again acknowledges the transmission and waits for 8 bits data which shall be written to the specified register address. After the slave acknowledges the data byte, the master generates a stop signal and terminates the writing protocol.

Table 10. I2C Write

| SI   |   | Sla | ive | Add | dres | ss | R<br>W | SAC      |   |   | Re | gist<br>(( | er A<br>Ox0 |   | res | s | SAC |   |   |   |   | Dat<br>0x4 |   |   |   | SAC      | STO |

|------|---|-----|-----|-----|------|----|--------|----------|---|---|----|------------|-------------|---|-----|---|-----|---|---|---|---|------------|---|---|---|----------|-----|

| AZ - | 0 | 0 0 | 1   | 1   | 0    | 0  | 0      | <b>X</b> | 0 | 0 | 0  | 0          | 1           | 0 | 1   | 0 |     | 0 | 0 | 0 | 0 | 0          | 0 | 0 | 1 | <b>X</b> | Р   |

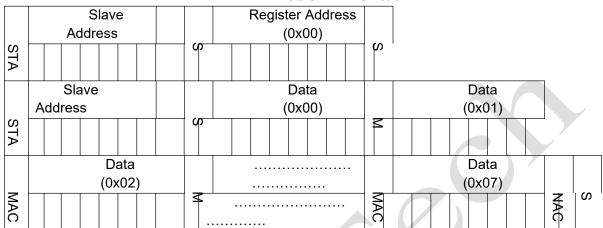

### 13.2.5 I2C Read

I<sup>2</sup>C write sequence consists of a one-byte I<sup>2</sup>C write phase followed by the I<sup>2</sup>C read phase. A start condition must be generated between two phase. The I<sup>2</sup>C write phase addresses the slave and sends the register address to be read. After slave acknowledges the transmission, the master generates again a start condition and sends the slave address together with a read bit (R/W=1). Then master releases the bus and waits for the data bytes to be read out from slave. After each data byte the master has to generate an acknowledge bit (ACK = 0) to enable further data transfer. A NACK from the master stops the data being

transferred from the slave. The slave releases the bus so that the master can generate a STOP condition and terminate the transmission.

The register address is automatically incremented and more than one byte can be sequentially read out. Once a new data read transmission starts, the start address will be set to the register address specified in the current I<sup>2</sup>C write command.

Table 11. I2C Read

## 14 Registers

### 14.1 Register Map

The table below provides a list of the 8-bit registers embedded in the device and their respective function and addresses.

Table 12. Register Map

| Addr. | 7                                                                           | 6         | 5              | 4 | 3 | 2 | 1 | 0         | Access    |  |

|-------|-----------------------------------------------------------------------------|-----------|----------------|---|---|---|---|-----------|-----------|--|

| 00H   | Data Out                                                                    | Read only |                |   |   |   |   |           |           |  |

| 01H   | Data Output X MSB Register XOUT[15:8]                                       |           |                |   |   |   |   |           | Read only |  |

| 02H   | Data Output Y LSB Register YOUT[7:0]                                        |           |                |   |   |   |   |           | Read only |  |

| 03H   | Data Output Y MSB Register YOUT[15:8]                                       |           |                |   |   |   |   | Read only |           |  |

| 04H   | Data Output Z LSB Register ZOUT[7:0]  Data Output Z MSB Register ZOUT[15:8] |           |                |   |   |   |   |           | Read only |  |

| 05H   |                                                                             |           |                |   |   |   |   |           | Read only |  |

| 0AH   |                                                                             |           | ODR[1:0] MOD E |   |   |   |   |           | R/W       |  |

| 0BH   | SOFT_<br>RST SET/RESET<br>MODE                                              |           |                |   |   |   |   | R/W       |           |  |

| 0CH   | Chip ID                                                                     |           |                |   |   |   |   | Read only |           |  |

<sup>\*</sup> Warning: All undefined bits in the register must write '0', if it is written '1', the function and performance of the chip will be greatly affected, even the chip may be damaged.

### 14.2 Register Definition

### 14.2.1 Output Data Register

Registers  $00H \sim 05H$  store the measurement data from each axis magnetic sensor in continuous-measurement. In the Normal measurement mode, the output data is refreshed periodically based on the data update rate ODR setup in control register 1. The data stays the same, regardless of reading status through  $I^2C$ , until new data replaces them. Each axis has 16 bit data width in 2's complement, i.e., MSB of 01H/03H/05H indicates the sign of each axis.The output data of each channel saturates between -32768 and 32768.

Table 13. Output Data Register

| Addr. | 7                                                                           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------------------------------------------------------------------------|---|---|---|---|---|---|---|

| 00H   | Data Output X LSB Register XOUT[7:0]                                        |   |   |   |   |   |   |   |

| 01H   | Data Output X MSB Register XOUT[15:8]                                       |   |   |   |   |   |   |   |

| 02H   | Data Output Y LSB Register YOUT[7:0]  Data Output Y MSB Register YOUT[15:8] |   |   |   |   |   |   |   |

| 03H   |                                                                             |   |   |   |   |   |   |   |

| 04H   | Data Output Z LSB Register ZOUT[7:0]                                        |   |   |   |   |   |   |   |

| 05H   | Data Output Z MSB Register ZOUT[15:8]                                       |   |   |   |   |   |   |   |

#### 14.2.2 Control Registers

Two 8-bits registers are used to control the device configurations.

Control register 1 is located in address 0BH, it set soft reset(SOFT\_RST), enable the feature of automatic set/reset.

Control register 2 is located in address 0AH. it sets the operational modes (MODE) and the output data rates (ODR).

The ODR bit can transfer data rates of output in the device, the four output data rates are 10Hz \, 50Hz \, 100Hz and 200Hz. The output data rates correspond to the measurement cycle frequency one by one. By setting the ODR, the power consumption of the device decreases with the decrease of output data rates. The default ODR after Power-on-Reset (POR) is 200Hz.

The MODE bit can transfer mode of operations in the device, the two modes are Standby and Normal. The Standby mode only support the basic functions of analog and digital without any measurement. The Normal mode runs in the measurement cycle state, and the cycle frequency is controlled by the ODR bit. The default mode after Power-on-Reset (POR) is standby. There is no any restriction in the transferring between the modes.

SET/RESET function is realized by generating pulse current between sensors S/R+ and S/R-. When a set pulse is applied, the component of the output and external magnetic field strength on the sensitive axis of the magnetometer is a straight line with a positive slope. When a reset pulse is applied, the component of the output and external magnetic field strength on the sensitive axis of the magnetometer is a straight line with a negative slope. All in all , the function of SET/RESET is to restore the initial state of AMR built-in magnetic field.

Table 14. Control Register

|                     | Addr      | 7                                | 6 | 5            | 4 |          | 3   | 2               | 1       |         | 0  |

|---------------------|-----------|----------------------------------|---|--------------|---|----------|-----|-----------------|---------|---------|----|

|                     | 0BH       | SOFT_RST                         |   |              |   |          | SET |                 | Γ/RESET |         |    |

|                     |           |                                  |   |              |   |          |     |                 |         |         |    |

| Control<br>Register | Reg.      | Definition                       |   | 0            |   |          |     | 1               |         |         |    |

| 1                   | SOFT_RST  | Reset registers to default value |   | Normal       |   |          |     | Reset and Clear |         |         |    |

|                     | Reg.      | Definition                       |   | 00           |   | 01       |     | 10              |         | 11      |    |

|                     | SET/RESET | SET/RESET mode                   |   | SET/RESET    |   | SET      |     | NO<br>SET/RESET |         | Reserve |    |

|                     | Addr      | 7                                | 6 | 5            | 4 |          | 3   | 2               | 1       |         | 0  |

|                     | 0AH       |                                  |   | ODR[1:       |   | ODR[1:0] | ]   |                 |         | MODE    |    |

| Control             |           |                                  |   |              |   |          |     |                 |         |         |    |

| Register            | Reg.      | Definition                       |   | 0            |   |          | 1   |                 |         |         |    |

| 2                   | Mode      | Mode Control                     |   | Standby      |   |          |     | Normal          |         |         |    |

|                     | Reg.      | Definition                       |   | 00 (default) |   | 01       |     | 10              |         | 11      |    |

|                     | ODR       | Output data rates                |   | 200Hz        |   | 100Hz    |     | 50Hz 10         |         | 10H     | Ηz |

Note: During initialization, register 0AH(bit7~bit4) must be written 0100b

Soft Reset can be done by changing the register SOFT\_RST to set. Soft reset can be invoked at any time of any mode. For example, if soft reset occurs at the middle of Normal mode reading, VCM1193L immediately switches to standby mode due to all registers are reset to "00" in default.

SOFT\_RST: "0": Normal "1": Soft reset, restore default value of all registers.

#### 14.2.3 Chip ID Register

This register is chip identification register. It returns 0x82.

**Table 15. Chip ID Register**

| Addr. | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|---|---|---|---|---|---|---|

| 0CH   | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

## For more information, customized systems, etc., please contact us.

## VTran Tech (Changzhou) Co., Ltd.

Changzhou Telephone Number: 0519-88856618 Shanghai Telephone Number: 021-68583580

Business Inquiries: sales@vtrantech.com

Company Website:

Changzhou Office Address: A1-802, Science and Education City, Wujin District, Changzhou ShangHai office address: 5B, building 1, no. 26 QiuYue Road, PuDong District, ShangHai

ShenZhen office address: 1517, Block A, Burton Building, Xili Chaguang Road, Nanshan District, Shenzhen

The information contained in this report is subject to change without notice.

VTran Tech strives to ensure the correctness of this information, but does not assume any responsibility for any technical, editorial, or other errors herein contained.

The release of rights belongs to VTran Tech.

© Copyright 2020 VTran Tech CORPORATION LIMITED. All rights reserved.

20 / 20